Supraskite DIP

DIP yra įskiepis. Tokiu būdu supakuoti lustai turi dvi kaiščių eiles, kurias galima tiesiogiai privirinti prie DIP struktūros lustų lizdų arba privirinti prie suvirinimo vietų su tuo pačiu skylių skaičiumi. Labai patogu atlikti PCB plokštės perforuotą suvirinimą ir gerai suderinama su pagrindine plokšte, tačiau dėl didelio pakuotės ploto ir storio, kaištį įdėjimo ir išėmimo metu lengva pažeisti, todėl patikimumas yra prastas.

DIP yra populiariausias įskiepių korpusas, kurio taikymo sritis apima standartinius loginius IC, atminties LSI, mikrokompiuterių grandines ir kt. Mažo profilio korpusas (SOP), gautas iš SOJ (J tipo kontaktų mažo profilio korpuso), TSOP (plono mažo profilio korpuso), VSOP (labai mažo profilio korpuso), SSOP (sumažinto SOP), TSSOP (plono sumažinto SOP) ir SOT (mažo profilio tranzistorių), SOIC (mažo profilio integrinių grandynų) ir kt.

DIP įrenginio surinkimo konstrukcijos defektas

PCB korpuso anga yra didesnė nei įrenginio

PCB kištukų ir korpuso kaiščių skylės brėžiamos pagal specifikacijas. Kadangi plokštės gamybos metu skylėse turi būti vario padengimo poreikis, bendras tolerancijos lygis yra plius arba minus 0,075 mm. Jei PCB korpuso skylė yra per didelė nei fizinio įrenginio kaištis, įrenginys gali atsilaisvinti, nepakanka skardos, gali kilti oro suvirinimo problemų ir kitų kokybės problemų.

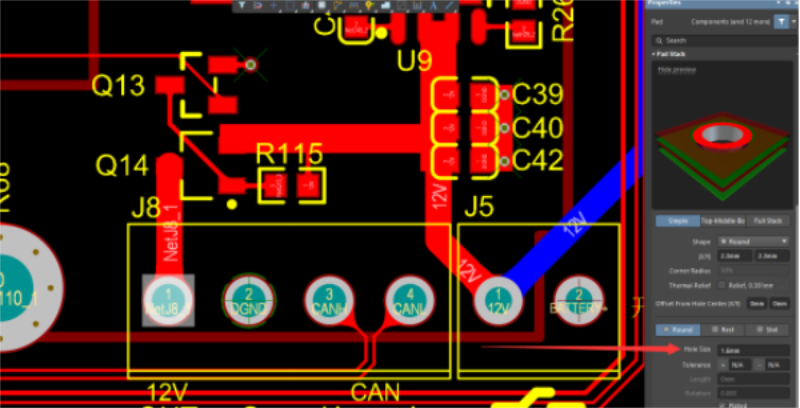

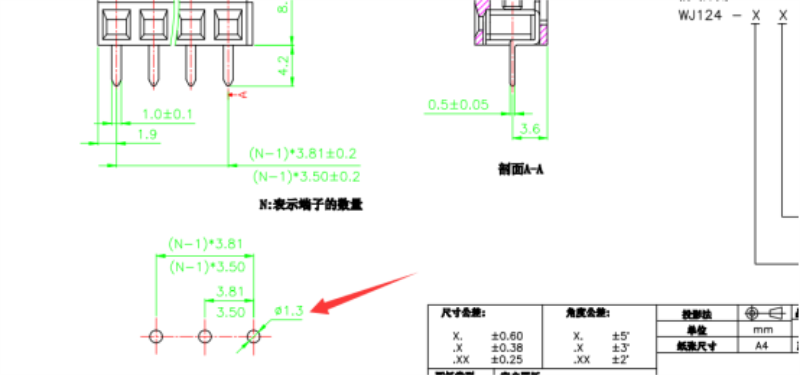

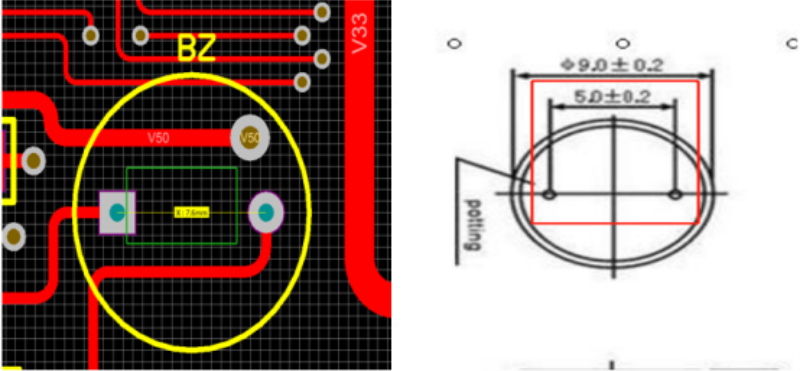

Žr. paveikslėlį žemiau, naudojant WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) įrenginio kaiščio skersmuo yra 1,3 mm, PCB pakuotės anga yra 1,6 mm, o per didelė anga gali sukelti per didelį suvirinimo bangos ilgį ir suvirinimo laiką.

Prisegtame paveikslėlyje įsigykite WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) komponentus pagal projektavimo reikalavimus, 1,3 mm kaištis yra teisingas.

PCB korpuso skylė yra mažesnė nei įrenginio

Įkišama, bet skylės vario neturi, jei tai yra viengubos ir dvigubos plokštės, šiuo metodu galima naudoti viengubas ir dvigubas plokštes, kurios praleidžia elektrą išorėje, o litavimas gali būti laidus; Daugiasluoksnės plokštės įkišama skylė yra maža, o PCB plokštę galima perdaryti tik tuo atveju, jei vidinis sluoksnis praleidžia elektrą, nes vidinio sluoksnio laidumo negalima ištaisyti gręžiant.

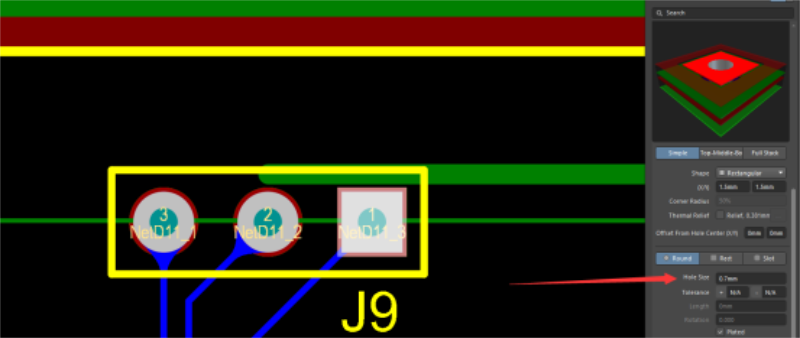

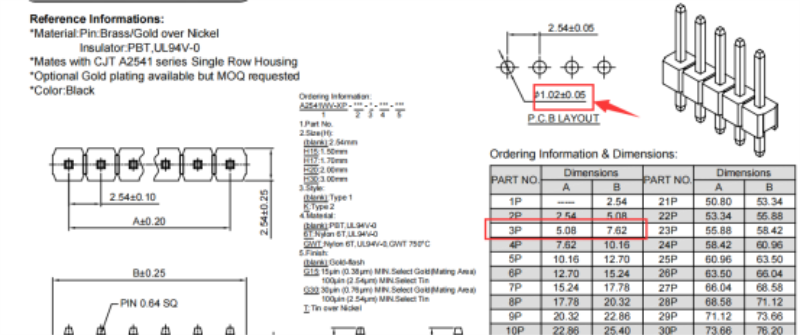

Kaip parodyta paveikslėlyje žemiau, A2541Hwv-3P_A2541HWV-3P (CJT) komponentai yra perkami pagal projektavimo reikalavimus. Kaiščio skersmuo yra 1,0 mm, o PCB sandarinimo pagalvėlės skylės skersmuo – 0,7 mm, todėl jo neįmanoma įdėti.

A2541Hwv-3P_A2541HWV-3P (CJT) komponentai yra perkami pagal projektavimo reikalavimus. 1,0 mm kaištis yra tinkamas.

Pakuotės kontaktų atstumas skiriasi nuo įrenginio atstumo

DIP tipo įrenginio PCB sandarinimo pagalvėlė ne tik turi tokią pačią angą kaip ir kaištis, bet ir tokį patį atstumą tarp kaiščių skylių. Jei atstumas tarp kaiščių skylių ir įrenginio yra nevienodas, įrenginio negalima įdėti, išskyrus dalis su reguliuojamu atstumu tarp kojų.

Kaip parodyta paveikslėlyje žemiau, PCB pakuotės kaiščių skylių atstumas yra 7,6 mm, o įsigytų komponentų kaiščių skylių atstumas yra 5,0 mm. 2,6 mm skirtumas lemia, kad įrenginys tampa netinkamas naudoti.

PCB pakuotės skylės yra per arti

PCB projektuojant, braižant ir pakuojant būtina atkreipti dėmesį į atstumą tarp kaiščių skylių. Net jei galima pagaminti pliką plokštę, atstumas tarp kaiščių skylių yra mažas, todėl banginio litavimo metu surinkimo metu lengva sukelti alavo trumpąjį jungimą.

Kaip parodyta paveikslėlyje žemiau, trumpąjį jungimą gali sukelti mažas atstumas tarp kontaktų. Yra daug priežasčių, kodėl litavimo metu gali atsirasti trumpasis jungimas. Jei projektavimo pabaigoje iš anksto būtų išvengta surinkimo problemų, problemų dažnumas būtų sumažintas.

DIP įrenginio kontaktų problemos atvejis

Problemos aprašymas

Suvirinus DIP gaminį bangos keteros metodu, nustatyta, kad ant fiksuotos tinklo lizdo kojelės litavimo plokštės, kuri priklausė oro suvirinimui, labai trūksta alavo.

Problemos poveikis

Dėl to pablogėja tinklo lizdo ir PCB plokštės stabilumas, o gaminio naudojimo metu bus veikiama signalinio kaiščio kojelės jėga, kuri galiausiai sukels signalinio kaiščio kojelės prijungimą, paveikdama gaminio veikimą ir sukeldama gedimo riziką vartotojams.

Problemos pratęsimas

Tinklo lizdo stabilumas prastas, signalo kaiščio ryšio našumas prastas, yra kokybės problemų, todėl tai gali kelti pavojų vartotojui, o galutiniai nuostoliai neįsivaizduojami.

DIP įrenginio surinkimo analizės patikrinimas

Su DIP įtaisų kontaktais susijusi daug problemų, ir daugelį svarbių dalykų lengva ignoruoti, todėl galiausiai plokštė sugenda. Taigi, kaip greitai ir visam laikui išspręsti tokias problemas?

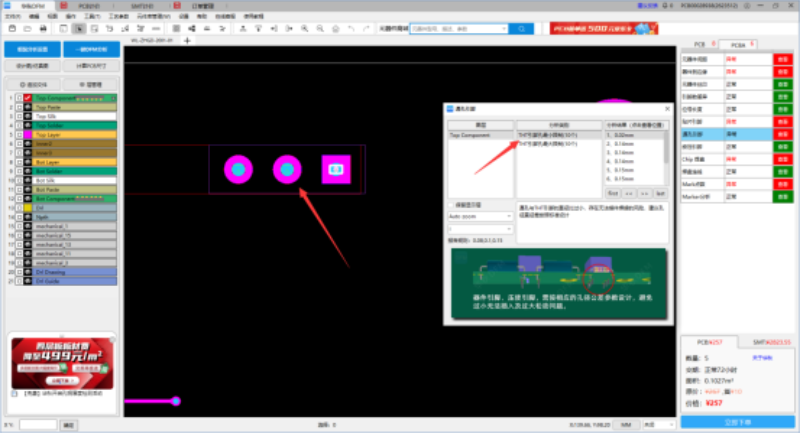

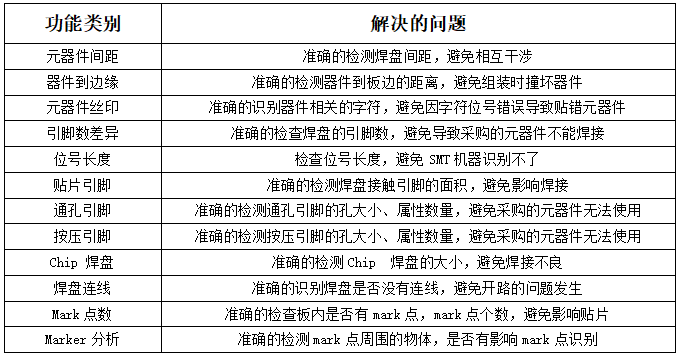

Čia, mūsų CHIPSTOCK.TOP programinės įrangos surinkimo ir analizės funkcija gali būti naudojama atlikti specialią DIP įtaisų kontaktų patikrą. Tikrinimo elementai apima kiaurymių kontaktų skaičių, didelę THT kontaktų ribą, mažą THT kontaktų ribą ir THT kontaktų atributus. Tikrinimo elementai iš esmės apima galimas DIP įtaisų projektavimo problemas.

Užbaigus PCB projektavimą, PCBA surinkimo analizės funkcija gali būti naudojama iš anksto aptikti projektavimo defektus, išspręsti projektavimo anomalijas prieš gamybą ir išvengti projektavimo problemų surinkimo procese, atidėti gamybos laiką ir švaistyti tyrimų bei plėtros išlaidas.

Jo surinkimo analizės funkcija turi 10 pagrindinių elementų ir 234 smulkių elementų tikrinimo taisykles, apimančias visas galimas surinkimo problemas, tokias kaip įtaisų analizė, kaiščių analizė, kontaktų analizė ir kt., kurios gali išspręsti įvairias gamybos situacijas, kurių inžinieriai negali iš anksto numatyti.

Įrašo laikas: 2023 m. liepos 5 d.